Chiplets’ Day Is Here, but Their Ecosystem Is Still Evolving

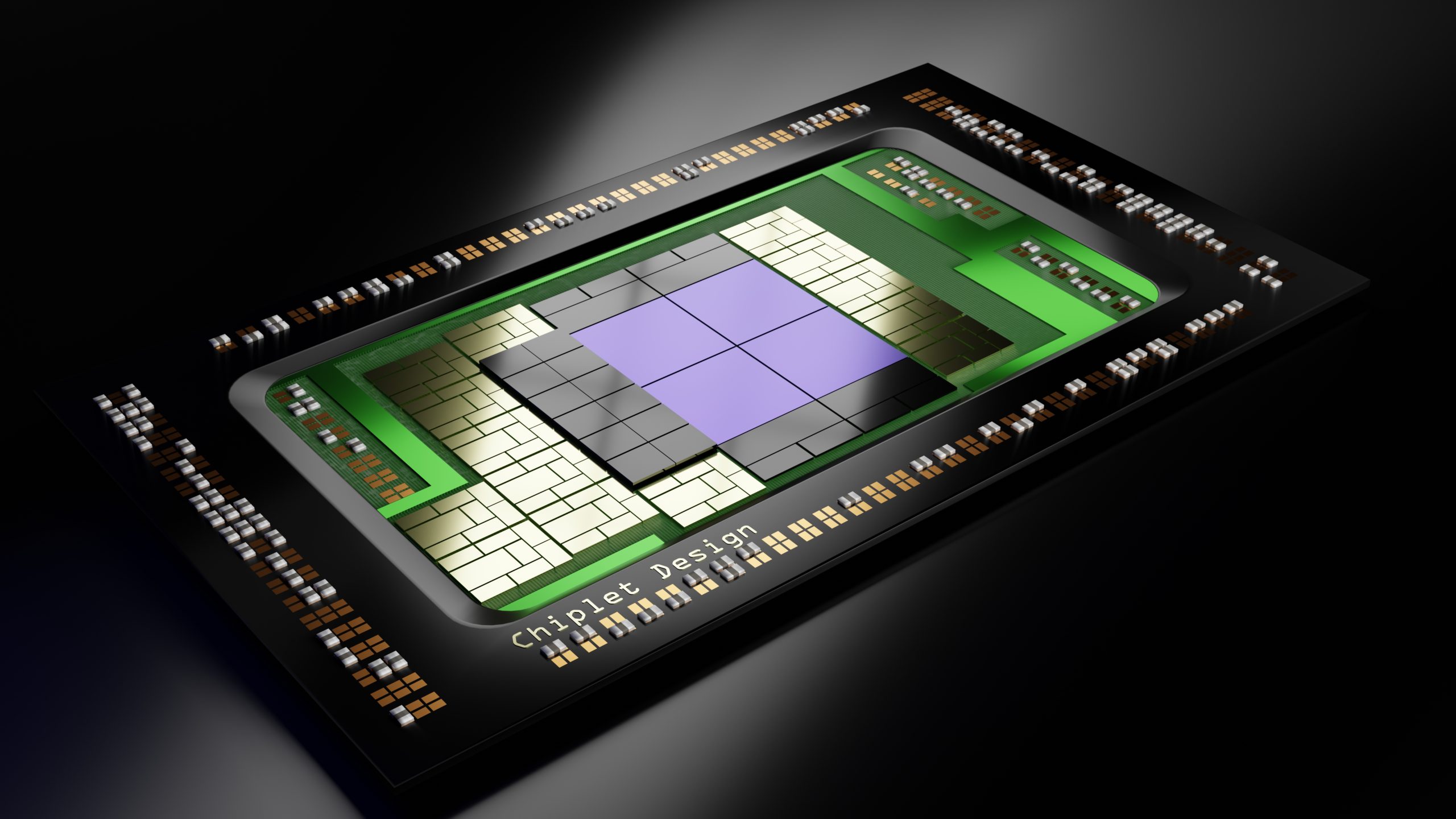

In the post-Moore’s Law era, chiplets – whose future implementation Gordon Moore also predicted – are expected to deliver high performance and area utilization, together with low power consumption and cost. Conceptually similar solutions, such as multi-chip modules and systems-on-chip, have been around for many years. The chiplet takes this concept a step further, creating a vehicle for silicon-level reuse of IP blocks. As a result, chiplets are widely recognized as a key technology going forward.

Currently, chiplets are available only in vertically integrated companies, but firms at every level of the industry are highly focused on figuring out how they can play in the chiplet market once availability widens. Outsourced semiconductor assembly and test providers (OSATs) are looking to purchase known good die (KGD) in order to create their own chiplets. Defined as chips that have been fully tested to meet a given specification before being placed into their packages, KGD will be critical to the future of chiplet manufacturing. Without KGD, the package in a chiplet-based architecture could suffer from low yield or experience field failure. Moreover, if the chiplet utilizes a ceramic substrate, these can be costly to replace if the final package is faulty because of a bad chip.

One key issue with chiplets is how to manage multiple die with different coefficients of thermal expansion (CTE) on the same package with tight interconnect tolerances. To address this and other related challenges, chiplet/multi-die-package integration is a primary component of the industry’s Heterogeneous Integration Roadmap (HIR). Sponsored by industry organizations and their members from throughout the global electronics business, the HIR was developed to lay out a long-term vision for the electronics industry. Chiplets offer advantages for scaling and yield in a range of applications and are a vital aspect of HI as “More than Moore” evolves. The 2021 edition of the HIR notes that a “chiplet initiative” is under way, utilizing different packaging technologies for disparate system applications.

The U.S. government has also taken a significant interest in microelectronic packaging, seeking to onshore packaging, as well as chip fabrication, for supply chain and IP security. The State-of-the-art Heterogeneous Integration Program (SHIP) was established by the Office of the Under Secretary of Defense (OUSD) as part of the Trusted and Assured Microelectronics Program to develop a sustainable business and operational model for addressing government needs in microelectronics packaging. Intel and Qorvo won awards in 2020 to develop next-generation multichip packages, with Intel leading the SHIP Digital effort and SHIP RF being led by Qorvo. The second phase of the program will develop prototypes of multichip packages and accelerate advancement of interface standards, protocols and security for heterogeneous systems.

While the overall chiplet ecosystem is still being determined, some players have already established a market position that will stand them in good stead as these efforts progress. For more than 40 years, Gel-Pak has been a leader in protecting KGD throughout internal processing and handling as well as shipping, ensuring the die remain good until they arrive at their destination. Gel-Pak’s team of engineers and scientists are continually working on developing new, advanced polymers and formfactors for safe handling of chiplets.

We are currently collaborating with customers on more efficient ways to process KGD for chiplet packages. To that end, we have designed a new universal carrier for device handling and transport applications. Using a proprietary new film based on our Vertec® technology, the recently introduced BTXF product uses non-adhesive properties of a micro-textured elastomer laminated to a JEDEC tray to hold components in place. Our BTXF products can be used for internal processing, kitting, and shipping and allow for easy picking and repicking of components.

We are excited to see how the chiplet world develops, and we look forward to working with companies and partners throughout the industry to make sure they stay safe.

If you’re interested in learning more about how our line of Gel-Pak products can transport your delicate chiplet devices, we’ll be presenting at the 2023 Chiplet Summit on Wednesday, January 25th from 3:15-4:15 PM in B-102.